Lab Workshop on SoC Verification - Batch II

About the Program

Design Verification in VLSI is a critical and time-intensive step in the product development process. Its primary goal is to ensure that the product or system design complies with specified standards and requirements. In fact, it typically accounts for about 80% of the total time allocated for the product development process. Many foundries place significant emphasis on testing and verification, which are crucial at every stage of VLSI design.

System Verilog is a hardware description and verification language that plays a crucial role in the field of electronic design automation (EDA) and integrated circuit (IC) design. It's an extension of Verilog, which was originally developed for digital design and simulation. System Verilog adds powerful features specifically designed to facilitate verification, such as enhanced data types; object oriented programming capabilities, assertions, constraints, coverage and parallel or concurrent threads. This make system Verilog a vital tool in the development of complex digital systems

This course offers a comprehensive introduction to the primary enhancements that System Verilog brings to the Verilog hardware description language (HDL). It also illustrates the advantages of these new features and illustrates how design and verification processes can become more efficient and productive with the utilization of System Verilog constructs.

Perquisites for the program

Verilog HDL Knowledge / Lab Workshop on FPGA Architecture and Programming using Verilog HDL /Lab Workshop on ARM Based SoC Design/Lab Workshop on Advanced ARM SoC Design.

Who should attend? : Engineering students, recent graduates and young professionals with back ground in Digital Electronics

24X7 Self-paced using Recorded Lectures

Lab Timings: 5 pm to 11 pm on weekdays 10 am to 11 pm on weekends

Credits : 03 Credits

Certificate Criteria: 50 % for assignments and 50 % for exit test

Contents: Lectures, demos, Lab experiments and Mini project

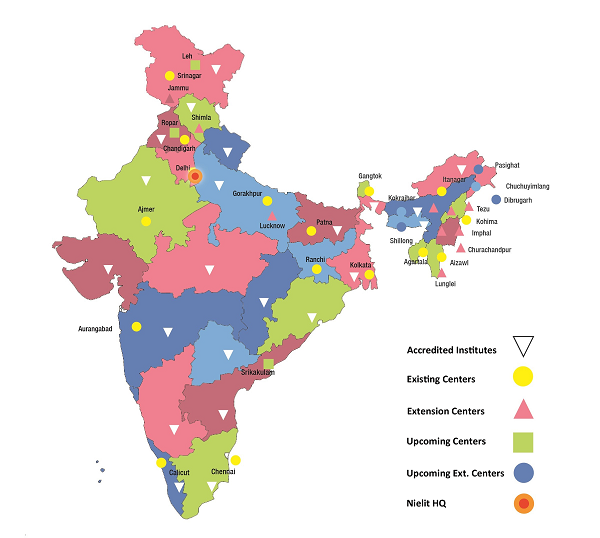

Mode of Delivery: Theory sessions shall be delivered through online mode using pre-recorded lectures. Lab demo (recorded) and live sessions shall be delivered through online mode by NIELIT Calicut. Lab experiments and Mini Project shall be done through the Remote SMART lab at NIELIT Calicut.

Major topics:

- Introduction to Verification and System Verilog.

- Data Types in System Verilog

- Procedural and Flow Control statement in System Verilog

- System Verilog FORK and JOIN statements.

- Object oriented Programming Concepts in System Verilog.

- Randomization and Constraints in System Verilog.

- Assertions in System Verilog

- Verification of combinational and Sequential Circuits using System Verilog.

- Verification of IPs based on AHB Lite/ APB/AXI using system Verilog.

Important Dates

| Event | Date |

|---|---|

| Registration closing date | First Come First Served Basis Will be closed once batch is full |

| Sharing of Course link | 24-03-2024 (will be mailed to Registered Email) |

| Course Start date | 25-03-2024 |

| Course Duration | 65 Hours (13 hours theory and 52 hours lab) |