Lab Workshop Advanced ARM SoC Design - Batch III

About the Program

24X7 Self-paced using Recorded Lectures

Objective

The objective of the course is to provide a thorough theoretical understanding and practice with ARM based SoC design and Synthesis of peripherals using EDA tools.

Target Audience:

BE/B.Tech (ECE/EEE/AEI/CSE/IT/Biomedical/Medical Electronics, Mechatronics and allied branches) / M.Sc. (Electronics/CS) or Ongoing with 3rd semester completed.

This Workshop is intended to give participants a quick start and hands on practice needed for implementing cutting edge projects especially in domains like VLSI, Embedded Systems, Computer Architecture, Communication, DSP, Control and automation Biomedical etc., targeting FPGA /ASIC.

Who should attend?

Engineering students, recent graduates and young professionals with back ground in Digital Electronics

Certificate Criteria: 50 % for assignments and 50 % for exit test

Contents: Lectures, demos, Lab experiments and Mini project

Mode of Delivery:

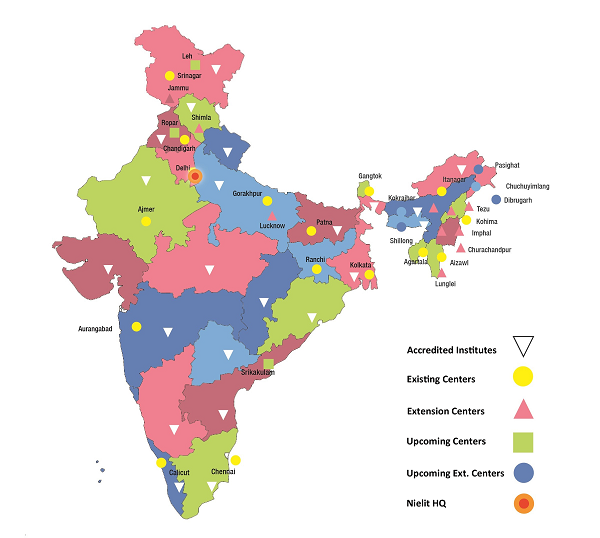

Theory sessions shall be delivered through online mode using recorded lectures by NPTEL. Lab demo (recorded) and live sessions shall be delivered through online mode by NIELIT Calicut. Lab experiments and Mini Project shall be done using resources at participant’s computer using Freeware Tools/Evaluation Version of Industry standard EDA Tools or in our Remote Hardware Lab

Perquisites for the program:

- Verilog HDL Knowledge / Lab Workshop on FPGA Architecture and Programming using Verilog HDL /Lab Workshop on ARM Based SoC Design.

Major Topics

- Fundamental of Programmable Logic

- FPGA Architecture

- FPGA Design Flow

- ARM M0 Architecture

- AHB Light bus architecture

- Assembly Programing for ARM

- ARM M1 & M3 Architecture

- Building a System on Chip- Integrating AHB peripherals to ARM using Verilog HD for UART, Timer, MEMORY, GPIO etc.

- Synthesis of AHB peripherals on the ARTY A7 FPGA Kits

- Synthesis of UART, Timer, MEMORY, GPIO etc.

- ZYNQ Architecture and Demo of ZYNQ Programming.

Important Dates

| Event | Date |

|---|---|

| Registration closing date | First Come First Served Basis Will be closed once batch is full |

| Sharing of Course link | (will be mailed to Registered Email) |

| Course Start date | 23-03-2026 |

| Course Duration | 105 Hours:- 15 Hours Theory and 90 Hours Lab (Remote Hardware Lab) (8 Weeks)- 4 Credits Course. (This is as per KTU and NDU Guidelines) |

Frequently Asked Questions (FAQ)

Support Team

- Workshop Coordinator: Mr Sreejeesh, STO . Email :sree[at]calicut[dot]nielit[dot]in. , sreejeesh[at]nielit[dot]gov[dot]in. Ph# 94477 69756

- For Queries/Support : Ms Nanditha Varma, STO . Email :nanditha[at]calicut[dot]nielit[dot]in.