LMS based Embedded System Design on FPGA - Instruction Enhancement Program(IEP), Covering Swadeshi Microprocessors

IEP Schedule: 7th April 2021 and 12th April 2021

Starting Date : 7th April 2021

Timings : Live Session : 10 am to 12.00 noon (Theory)

Lab / Assignments can be submitted Online Learning Management Systems (Any Time)

Remote Lab Timing will be informed to selected participants ( Remote LAB will be available for first 100 eligible registrants)

Eligibility : Candidates qualified for the Semifinal of Microprocessor Challenge.

Selection Criteria : For the first thousand (1000) eligible registrants on a first come first served. It is requested that only one registrant per team may register, to ensure fair chance to all teams, registered for the challenge.

Registrants selected for IEP will be intimated by email

|

|

IEP LMS Link |

BACKGROUND OF स्वदेशी MICROPROCESSOR CHALLENGE

Under #AatmaNirbharBharat Abhiyan, there is a growing need for Swadeshi Compute Hardware, that shall be part of every Smart Device deployed in different domains, including Electronics for public utility services such as Surveillance, Transportation, Environmental condition monitoring, to commodity appliances like smart fans/ locks/ washing machines. In addition, with growing penetration of smart electronics in strategic areas including Space, Defense and Nuclear energy, the need for Swadeshi Compute Hardware is crucial. It is not just the cost or embargo that drives this need, but also the dependence on external vendors, long term sustenance, quick enhancements to suit the ever-growing requirements, and most-importantly Security, which drives #AatmaNirbharta in Hardware domain, as the only option.

Under Microprocessor Development Programme spearheaded by MeitY at C-DAC, IIT Madras and IIT Bombay, a family of 32-bit/ 64-bit Microprocessor has been designed from the scratch using Open Source ISA (Instruction Set Architecture), as a step towards meeting India’s future requirements of strategic/ commercial/ Industrial sector.

The Training will be imparted making use of Xilinx Artix7 35-T FPGA Boards.

Schedule

Duration : 5 Days

Tentative Timings : 10 am to 12.00 noon (Theory) Lab/Assignments can be submitted Online Learning Management Systems (Any Time)

Starting date : 7th April 2021

Syllabus

URL : https://innovate.mygov.in/swadeshi-microprocessor-challenge/

|

Day |

10.00 AM to 12.00 PM |

1.00 PM to 11.00 PM |

|

07-04-2021 |

Vega Peripherals - SPI , I2C and PWM (CDAC Trivandrum) |

Remote Lab Session |

|

08-04-2021 |

Interfacing Wireless Modems with Swadeshi Processors ( NIELIT Calicut) |

Remote Lab Session |

|

09-04-2021 |

AXI Bus Interfacing with SHAKTI (IIT Madras ) |

Remote Lab Session |

|

10-04-2021 |

Linux Porting on Swadeshi Microprocessors ( NIELIT Calicut) |

Remote Lab Session |

|

12-04-2021 |

Doubt clearing session (IIT Madras, CDAC Trivandrum & NIELIT Calicut) |

Remote Lab Session |

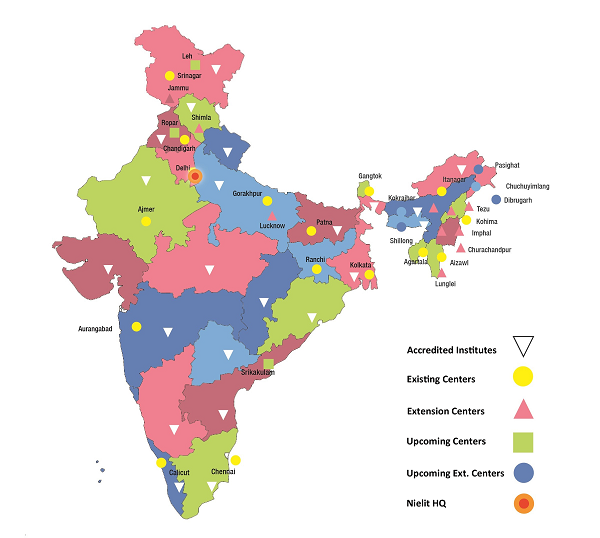

Contact Details : NIELIT Calicut (www.nielit.gov.in/calicut) .

Email : rajesh@calicut.nielit.in

Ph: 9447217649

WhatsApp : 9447769756