## <u>Course Name: A Level (1<sup>st</sup> Sem)</u> <u>Topic: Modes of Transfer contd.</u>

<u>Subject: CO</u> Date: 11-06-20

DMA Transfer > In a hardware with DMA mechanism, peripherals put their data on to their interfaces and get acknowledged. DMA controller now makes a request for graunting access of the FSB Common Bus) by using a line BR. BR. takes the request to CPU when CPU grants the access, it makes a line BG and 1. When BG is 1 DMA controller comes to know that the common bus can be used for transfers. Since it is a parallel processor, it uses all the line needed to read from or write in to the memory it places the address on address line date on input line add when woite enable is made 1 the data is transfer to memory. CPU is bypassed here by. Cycle stealing > By default every toansfer is a process and it should be accomplished by a CPU. Programmed 1/0 and interrupt initiated 1/0° are the two transfer method in which transfers are performed the same processor that is working for general operations but it DMA we have a seperate processor DMA controller for handling transfirs. Considering every succesful transfers that are handled by DMA are called stalen cycles since CPU is not much involved in these transfers this mechanism is called cycle, stealing.

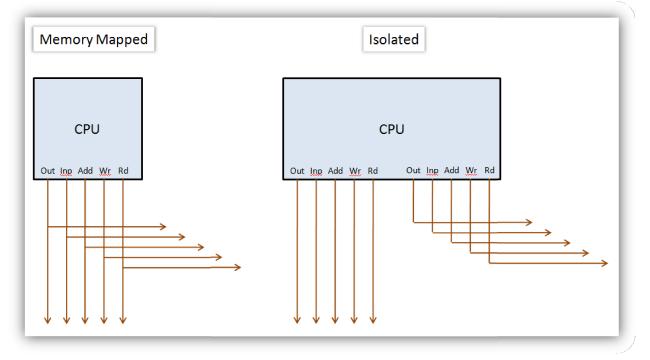

Isolated V/s Memory mapped > Usually CPU use the same line for x/w as memory chips use But when some kind of 1/0 transfer is involved the scanario forther changed there may be any of the following two method.

Memory mapped 110 -> In this method every line ( input, output, addres, read, write) are common for memory transfer & 110 transfer although it makes a burden on the involved line of the common bus CPU uses time divisions to perform both operation simulteniously. Isolated 110 - In this method the burden of common bus is reduced by increasing lines ACPU in this mechanism uses separate lines of trasfer for memory & 1/0. input, butput, read & write lines are seperate for memory \$1/0 and this arrangement is about all 1/0 transfers from memory transfors. Minwhile address lines are common to both

Interrupt Priority > little processing interrupt a flip flop R'is used to avoid some other intersupt Inside the one that is being processed but two interrupt different devices come at the same time, we need a priority to determine which will be process first. Following are two method for managing 1- Default priority of hardwards 2- Daisy chaining Mostly hardware manufactures define a perticular priority for the hardwore and this priority works when intersubts from those hardware occuris like wise peripherals like keyboard mouse etc. have lower priority than disk drives like FDD, HDD, etc. Stil in peripherals devices enjoy higher priority than printing devices. Dasichaining is another method that drametically handles the situation when two or more interrupt of some priority occure at a the same time in this method interrupting devices are scheduled to operate in an enclosed chain method. Every device is given equal slot to process its interrubt.

**NOTE:** This content is entirely written, diagrammed and prepared by me [Shashi Kant Mani Tripathi], hence you can write it all in your notes as it is.

## Assignment:

- **<u>1.</u>** Differentiate between Memory Mapped I/O and Isolated I/O.

- 2. Briefly describe Interrupt Priority.