Course Name: A Level (1<sup>st</sup> Sem)

<u>Topic: Multiplication Algorithm</u> <u>Date: 02-06-20</u>

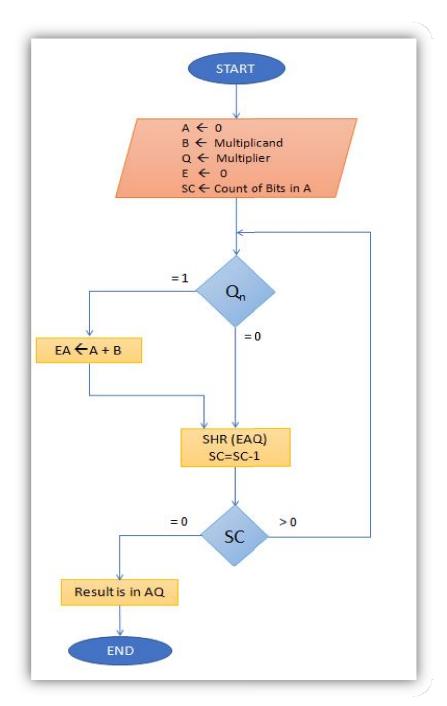

<u>Multiplication Algorithms:</u> Multiplication via pen and paper method is a compound practice of successive left shift and addition. But while working on digital hardware, the method is slightly different. The shift operation is a right shift instead of a left shift while the rest of the task is implemented in the following two ways:

**1.** Hardware Algorithm

2. Booth Algorithm

## **Hardware Algorithm:**

The multiplicand is stored in a register B and multiplier in Q. Another register A of same size is taken as to work like Accumulator.

A sequence counter SC is taken and initialized by the total count of bits in register B. A flip-flop E is used to store the excess carry while adding A with B. A complete set of EAQ participates in logical right shift.

With each shift operation the SC is decremented. When after many iterations, SC becomes absolutely zero; we stop the process and extract the result from AQ.

Consider the following flow-chart:

**Subject: CO**

## **NIELIT Gorakhpur**

The following example shows the entire operation with multiplicand (13) and multiplier (17).

The result that we get at last is 221:

| Accumulator [A] = 000000 |                        | E=0 |        | SC=6   |     |

|--------------------------|------------------------|-----|--------|--------|-----|

| $Q_n$                    | Description            | E   | Α      | Q      | SC  |

|                          |                        | 0   | 000000 | 010001 | 110 |

| 1                        |                        | 0   | 000000 |        |     |

|                          | EA ← A + B             |     | 001101 |        |     |

|                          |                        | 0   | 001101 | 010001 |     |

|                          | SHR (EAQ), SC ← SC − 1 | 0   | 000110 | 101000 | 101 |

| 0                        | SHR (EAQ), SC ← SC − 1 | 0   | 000011 | 010100 | 100 |

| 0                        | SHR (EAQ), SC ← SC − 1 | 0   | 000001 | 101010 | 011 |

| 0                        | SHR (EAQ), SC ← SC − 1 | 0   | 000000 | 110101 | 010 |

| 1                        |                        |     | 000000 |        |     |

|                          | EA ← A + B             |     | 001101 |        |     |

|                          |                        | 0   | 001101 | 110101 |     |

|                          | SHR (EAQ), SC ← SC − 1 | О   | 000110 | 111010 | 001 |

| 0                        | SHR (EAQ), SC ← SC − 1 | 0   | 000011 | 011101 | 000 |

## **Assignment:**

- **<u>1.</u>** Draw the flow chart of Hardware Algorithm.

- **2.** Multiply 23 and 21 using Hardware Algorithm.