VLSI for Beginners

Learn Core Skills

- What is VLSI ?

- Introduction to Hardware description languages (Verilog)

- Introduction to FPGA Architecture

- How to Program an FPGA (Demo)

Duration and Fees

- 5 Hours (5 Days/ 1 Hour)

- Theory-5 Hours

- Lab-2 Hours (on Request)

Course Fees: Nil/-

Starting Date - 10th of every month (in the case of public holidays, the last working day before the 10th is considered).

Last date of Registration: 8th of every month (in the case of public holidays, the last working day before the 8th is considered).

| Month | Starting date of Registration | Last Date of Registration | Course Starting Date |

|---|---|---|---|

| May | 11th Apr 24 | 8th May 24 | 10th May 24 |

| June | 13th May 24 | 6th June 24 | 10th June 24 |

| July | 11th June 24 | 8th July 24 | 10th July 24 |

The candidate has to complete a minimum of 50% of the course content, and an exit test is mandatory and is of qualifying nature.

Why would you enroll for this Course?

Foundation Course on which you can build on.

After learning the basics, you could move on to FPGA Design Prototyping, Verilog Programming, and Digital Design using FPGA.

Overview

This course is designed to introduce beginners to the basics of VLSI. The course will cover the scope and capabilities of VLSI Domain, Hardware description Languages introduction. How to program an FPGA will be illustrated. Students will also gain hands-on experience in programming FPGAs using popular tools like Vivado.(if special request for Remote Hardware Lab is requested upon completion of the course).

Mode of Delivery

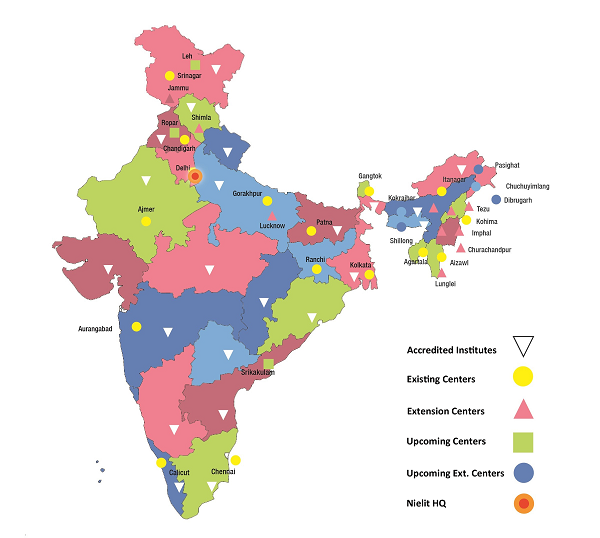

Platform: NIELIT LMS

These courses will be offered through LMS starting on the 10th day of every month. We will provide the course through LMS, a welcome mail will be sent on the previous day (9th day of every month) and the student will be allowed to attend the course for 5 days. A WhatsApp group will be started for every batch, which can be used for day to-day communication.

Hardware lab access will be provided (on demand) to students who have attended the course through the LMS and qualified in the exit test.

Prerequisites

Basic knowledge of digital circuits and programming concepts is recommended, but not mandatory. No prior experience with FPGAs or HDLs is required.

Certification

Attendance through the online portal and self-assessed Exercises will be considered for participation certificate.